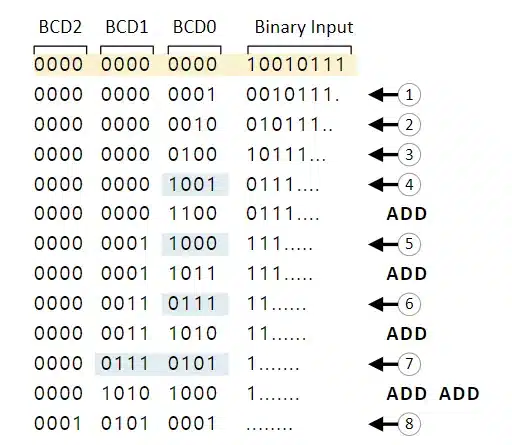

binary to bcd 예제를 verilog로 구현해보자. double dable algorithm을 이용할 예정이다. shift and add 3 algorithm이라고도 불리는데 말그대로 한칸씩 shift해주고 bcd의 한 숫자가 5보다 커지면 3을 더해주는 알고리즘이다. 만약 n bit을 변환하고 싶으면 n번 shifting해주면 된다.

double dabble algorithm 증명

필자는 사실 shift and add 3 algorithm라고 배웠는데 미국 형님들은 간지나게 “double dabble”이라고 부르는 모양이다. 사진은 그리려다가 미국 형님이 잘 그려놨길래 그냥 퍼왔다.

사진 출처 : https://www.realdigital.org/doc

5 이상이면 3을 더해주는 이유 :

binary number는 한번 shift를 할 때마다 2배가 커지게 된다. 5이상의 숫자를 shift해버리면 10을 넘어가버려서 bcd에 표현이 안된다. 처리를 해주어야하는데 bcd의 최대는 9이고 4bit binary의 최댓값은 15이기 때문에 이 차이인 6을 더해주어야 다음 bcd로 숫자 1이 넘어가게 되는 것이다. 우리가 구현할 알고리즘에서는 shift하기 전에 더해줄 것이므로 6의 절반인 3을 더해야 하는 것이다.

bcd –> 1001이 최대

실제로는 4bit binary 여서 –> 1111이 최대

우리의 목적은 1001이 되면 바로 다음 bcd에 1을 넘겨야됨.

다시 한번 설명하자면 1001이 되면 바로 다음으로 넘어가야하는데 실제로는 1111이 되야 다음으로 넘어가기 때문에 넘어갈 기미가 보이면 그냥 바로 차이인 3 (미래의 6)을 더해버려서 다음 bcd로 1을 줘버리겠다는 것이다. 백날 설명하는 것보다 코드를 보는 것이 빠를것이니 바로 코드를 보도록 하자.

구현

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

|

module bin2bcd(

input [3:0] bin,

output reg [7:0] bcd

);

integer i;

always @ (bin) begin

bcd = 0; //initiate the bcd. 안해주면 c언어처럼 쓰레기값 나옴

for(i = 0; i < 4; i = i+1) begin

if(bcd[3:0] >= 5) bcd[3:0] = bcd[3:0] + 3;

if(bcd[7:4] >= 5) bcd[7:4] = bcd[7:4] + 3;

bcd = {bcd[6:0], bin[3–i]}; // 반드시 if문 다음에 shift해줘야함.

end

end

endmodule

|

코드 설명

input으로 bin이 들어오고 output으로 bcd가 나간다. 해당 알고리즘은 n bit input이 들어오면 총 n번의 shifting이 일어나야하기 때문에 for문을 총 4번 돌도록 해주면 된다. 각각의 for문에서 bcd를 4bit단위로 검사해주고 만약 5보다 크면 3을 더해준다.

중요한 것은 반드시 if문이 수행된 후에 shift해주어야 되는데 이유는 마지막에는 5보다 크더라도 3을 더해주면 안되기 때문이다. 이유는 직접 해보면 바로 알 수 있다. 5는 bcd로 표현 가능하기 때문에 5를 출력해줘야 되는데 8을 출력해버린다.

문법 팁

integer는 반드시 always문 밖에 선언해주어야 에러가 안난다.

{a, b}는 결합 연산자인데 말그대로 합친다는 뜻이다. 예시로 {0101, 0011} 은 01010011 과 같다. bcd끝에다가 새로운 bin bit를 합치는데 이용하였다.

test bench 구성 및 시뮬레이션

|

1

2

3

4

5

6

7

8

9

10

11

12

13

|

module testbin2bcd;

reg [3:0] inp;

wire [7:0] out_my;

bin2bcd U0(.bin(inp), .bcd(out_my));

integer i;

initial begin

for(i = 0; i < 16; i= i+1) begin

#5 inp <= i;

end

end

endmodule

|

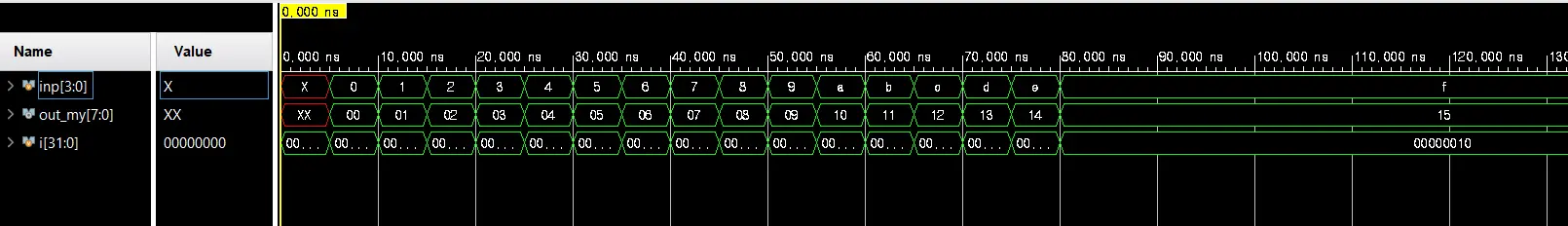

시뮬레이션 해보면 결과 값이 잘 나오는 것을 확인할 수 있다.

Leave a Reply

Your email is safe with us.